Details

HIGH DENSITY NETWORK APPLICATION CARD

The ExaNIC V5P is an FPGA based network application card, specifically optimized for lowlatency and high density datacenter applications.

The device is built around a powerful 16nm Xilinx Virtex Ultrascale Plus (VU5P) FPGA with 1.3M logic cells, packaged into a compact, production ready, half-height half-length, PCIe 8x form factor. It is also available in larger Ultrascale+ VU7P (1.7M logic cells) and VU9P (2.6M logic cells) variants. A PCIe 16x variant can be made available upon on request.

HIGH CAPACITY, LOW LATENCY MEMORY

An extensive memory hierarchy for complex, memory intensive applications.

The VU5P FPGA includes 4.5MB of block ram and 16.5MB of UltraRAM on chip for low latency access. The ExaNIC V5P incorporates an additional 28MB of QDR IV SRAM (30ns access latency using Exablaze QDR controller IP1), and 9GB of DDR4 DRAM for high throughput access. The DRAM is accessible via a 72 bit wide bus for maximum performance.

HIGH BANDWIDTH CONNECTIVITY

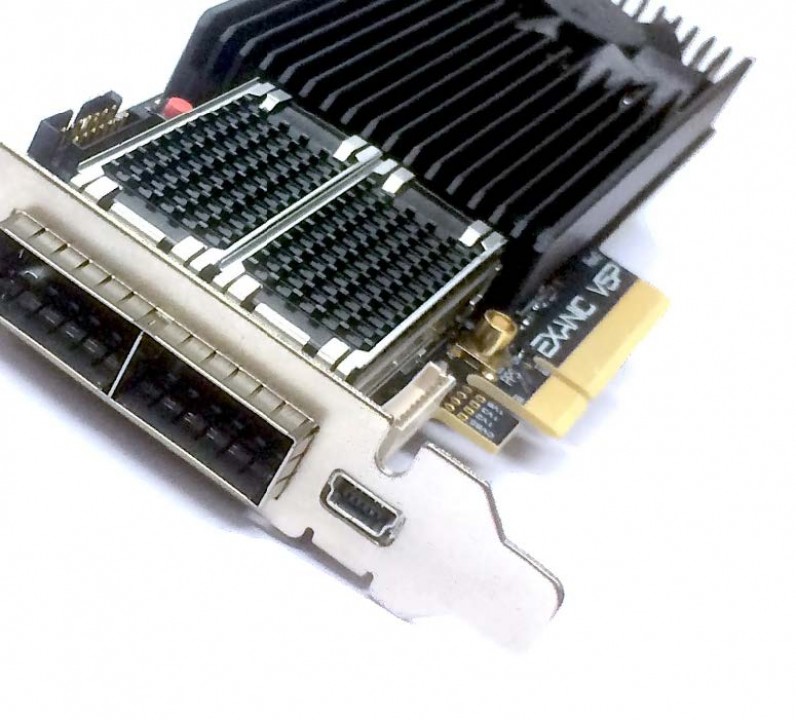

Dual QSFP28 ports provide up to 200Gbps of full duplex connectivity.

The dual QSFP28 cages offer high speed 2x40GbE or 2x100GbE connectivity. Using QSFP/QSFP28 breakout cables expands the connectivity to 8x10GbE/25GbE connections. This high density connectivity enables a range of high performance, directly connected network applications, bypassing the need for traditional switching and multiplexing requirements.

EXTENSIVE IP LIBRARY

Exablaze is a specialist in low-latency, high performance FPGA IP cores.

We provide to you the same high speed, low-latency IP blocks used in our world leading products. Available for the ExaNIC 5VP is a comprehensive, IP core library including:

- 100M/1G/10GbE PCS/MAC with 9.6ns (TX + RX) latency performance.

- Low latency, high throughput PCIe (Gen 3) DMA engine.

- Low latency QDR IV memory controller with 30ns access latency.

- Timing, signalling and register interfaces including I2C.

- Packet field extractor and frame multiplexor (with source code).

- Asynchronous FIFO and CDC modules (with source code).

Several example designs are also provided to help get design work started and completed quickly.

INTEGRATED SOFTWARE LIBRARY

In addition to a standard Linux driver, a transparent TCP and UDP acceleration library is included, as well as a library for low-level access.

Like all ExaNICs, the ExaNIC V5P functions out of the box as a high performance network adapter. The entire ExaNIC software library is available including the ExaSock sockets application acceleration system and the libexanic userspace direct accesses API. libexanic provides easy support for low latency packet TX/RX, managing FPGA state (through register access), and low latency TCP/UDP delegated sending operations for hybrid hardware/software applications. The ExaNIC V5P also supports fast and easy firmware updates (without requiring reboots), iPXE booting, and vital statistics monitoring (temperatures, fans, etc).

| Manufacturer | exablaze |

|---|---|

| Part No. | exanic-v5p |

| End of Life? | No |

| Width | 69 |

| Depth | 168 |

| Weight [Kg] | 0.20 |

| Bandwidth | PCS/MAC (TX + RX)2 : - 9.6ns (min) @ 10Gbps, - 1Gbps/100Mbps also supported |

| PCI Slot(s) | PCIe x8 Gen 4 @ 16.0 GT/s per lane |

| Port-Port Latency | Software latency (raw frame, ½RTT)1 : - 60 bytes – 780ns - 300 bytes – 999n |