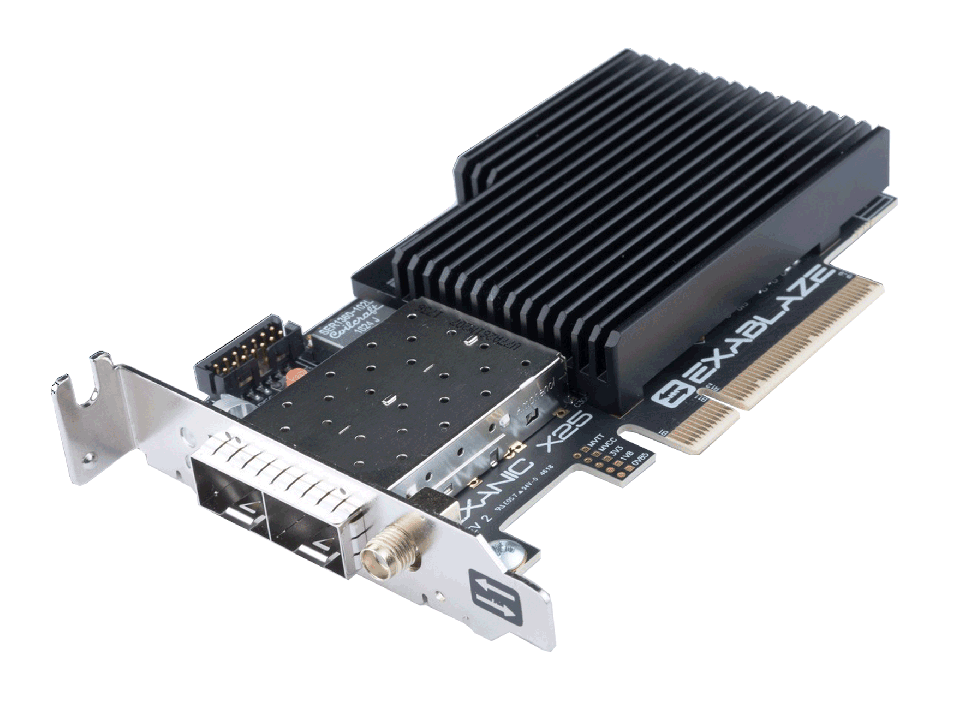

Cisco Exablaze ExaNIC X25

ULTRA LOW LATENCY DUAL-PORT 10/25GBE* NETWORK INTERFACE CARD

[NXN-K3P-2X=]Details

THE FASTEST NETWORK ADAPTER EVER BUILT

The ExaNIC X25 is specifically optimized for low latency operation.

It features software trigger-to-response latencies as low as 568ns. This is up to 20% faster than previous ExaNIC models, making it the fastest NIC ever built. Users will find that this drop-in replacement NIC accelerates tick-to-trade performance to previously unachievable speeds, increasing the efficacy and profitability of software based trading systems.

25GBE READY

The ExaNIC X25 is a pure FPGA based network adapter that is 25GbE ready.

FPGA network adapters extend the useful life of the device by allowing new features and peed enhancements to be downloaded into the device after deployment. For example, the ExaNIC X25 will support 25G Ethernet speeds through a firmware update. This will reduce capital expenditure on lengthy and difficult infrastructure upgrades.

Free and open source software interface

The device features an advanced free and open source software interface optimized for low latency network processing.

Features include: zero latency programmable receive steering, cut-through packet streaming, pre-loaded packet transmission, and TCP/IP acceleration.

Performance

Typical latency, raw frames:

64 bytes: 696ns

256 bytes: 897ns

Typical latency, raw frames with pre-loaded TX buffer:

64 bytes: 629ns

256 bytes: 665ns

Typical latency, UDP (using ExaSOCK sockets acceleration).:

14 bytes: 810ns

256 bytes: 1.1µs

Typical latency, TCP (using ExaSOCK sockets acceleration).:

14 bytes: 850ns

300 bytes: 1.1µs

ALL FPGA DESIGN

The ExaNIC X25 is built using the latest generation Xilinx Ultrascale+ FPGA.

It optionally ships with 4GB of DDR4 memory for custom use. It is a compact adapter in a lowprofile form-factor. Users can benefit from the pure FPGA design by offloading critical network processing functions directly into the NIC using our fast and powerful Firmware Development Kit (FDK), while maintaining the ease of use and administration of a production grade network adapter.

ADVANCED SOFTWARE PROGRAMMABILITY

The ExaNIC X25 provides the most powerful programmable software interface on the market.

Programmability features include:

- Zero Latency Cost Hardware Flow Steering - allowing users to steer and pre-filter important traffic to the right memory and CPU core with no latency penalty.

- Cut-Though Receive – this mechanism allows software to process packet fragments as they arrive from the wire, while packet tails are still in flight. This is especially effective for slow line speeds (e.g. 1GbE). The ExaNIC X25 software API puts users well ahead of traditional storeand-forward NIC designs to make better decisions, faster.

- ExaSOCK TCP/IP Acceleration - Unmodified sockets applications can benefit from the speed and power of the ExaNIC X25 using ExaSOCK. ExaSOCK is an in-place TCP/IP sockets acceleration system. ExaSOCK’s Extension API allows it to seamlessly interoperate with the X25’s Transmit Preloading feature described below.

- Pre-loaded packet transmit - The ExaNIC X25 allows users to preload transmit frames, saving 60ns from the transmit path. The X25 features enlarged packet transmit buffers allowing many more frames to be preloaded, leading to more versatile transmission choices.

- High resolution timestamps – 4ns timestamps are applied to every received packet and the most recently transmitted packet. The X25 also features out of the box support for IEEE1588 (PTP) and high-speed capture to disk using free and open source Exact-Capture software.

| Manufacturer | Cisco |

|---|---|

| Part No. | NXN-K3P-2X= |

| End of Life? | No |

| Preceeded By | EXANICX10 |

| Advanced Network Features | Advanced software API: - Cut-through receive (CT-RX) processing - Packet staging/pre-loading Zero-Latency Flow steering and flow hashing: - 128 IP rules per port - 64 MAC rules per port High rate packet capture: - Using free and open source Exact Capture software - Best paired with ExaDISK high rate capture NVMe drives FPGA Customization: - Xilinx KU3P Ultrascale+ device - 4GB DDR4 (32bit) variant available - Low-latency optimized Firmware Development Kit available - JTAG header on board (via apater cable) Timestamp resolution: - 4ns Timestamp availability: - All received (RX) frames - Most recent transmitted (TX) frame Time synchronization: - Host clock synchronization - PTP (IEE1588)(+/-5ns) - PPS in/out Time synchronization software: - Linux PTP (PTP4L) - PTPD (hardware timestamp branch) - exanic-clock-sync - Solarflare PTPD (SFPTP) |

| Bandwidth | 25GbE |

| Hardware Offloads | via FDK |

| Host OS Support | Linux x86_64 (all distributions) Windows |

| PCI Slot(s) | PCIe x8 Gen 3 @ 8.0 GT/s per lane |

| Ports | - 2x SFP28 - SMA for PPS in/out - JTAG port for firmware debug |

| Port-Port Latency | 4ns |

| Memory Capacity | 4GB Optional |